# Probabilistic Modelling of Variation in FGMOSFET Devices

#### Rawid Banchuin<sup>1</sup> and Roungsan Chaisricharoen<sup>2</sup>, Non-members

#### ABSTRACT

The analytical probabilistic modelling of random variation in the drain current of a Floating-Gate MOSFET (FGMOSFET) induced by manufacturing process variations has been performed. Both triode and saturation region operated FGMOSFETs have been considered. The results have been found to be very efficient since they can accurately fit the probabilistic distributions of normalized random drain current variations of the candidate triode and saturation FGMOSFETs obtained using the  $0.25\mu m$ level BSIM3v3 based Monte-Carlo SPICE simulations, where the variation of the saturation FGMOS-FET has been found to be more severe. These results also satisfy the goodness of fit test at a very high level of confidence and more accurately than the results of the previous probabilistic modelling attempts.

Using our results, many statistical parameters, probabilities and the objective functions, which are useful in statistical/variability aware analysis and design involving FGMOSFETs can be formulated. The impact of drain current variation upon the design trade-offs can be studied. It has been found that the occurrence of the drain current variation is absolutely certain. Moreover, the analytical probabilistic modelling and computationally efficient statistical/variability aware simulation of FGMOSFET based circuits can also be performed.

**Keywords**: FGMOSFET, Probabilistic Modelling, Saturation Region, Statistical/variability Aware Analysis and Design, Triode Region

#### 1. INTRODUCTION

FGMOSFET devices have been widely utilized in various analog/digital circuits and systems [1-14]. As with conventional MOSFETs, the performance of FGMOSFET based circuits and systems are deteriorated by circuit level random variations induced by variations in manufacturing processes, random dopant fluctuation, lithographic variation, variation

Manuscript received on July 27, 2016 ; revised on March 9, 2017.

in contact resistance and line edge roughness, among other factors. To handle these difficulties, the design of many FGMOSFET based circuits and systems has been done using the concept of statistical/variability aware design as proposed in numerous studies [4], [15-21].

The key circuit level parameter of both ordinary MOSFET and FGMOSFET devices is their drain current,  $I_D$ , because the variations in other parameters can be conveniently determined using the variation in  $I_D$ . Using  $\Delta I_D$  as a basis, analytical modelling of the  $\Delta I_D$  of a single transistor has been done in previous studies [22-23]. The obtained results are generic as they are applicable to any circuit and system. Modelling of the variation in any circuit level parameter can be done for statistical/variability aware analysis and design. Unfortunately, generic single transistor based studies have focused on ordinary MOSFET devices. Alternatively, most of the previous studies on the variability of FGMOSFET devices [24-32] have been done in a case by case manner focusing only on corresponding FGMOSFET based circuits. So, these results are not generic as they are applicable only to specific circuits. Later, analytical modelling of  $\Delta I_D$ for a single FGMOSFET device was done [33-34]. However, the resulting model in [33] was expressed in terms of the variance of  $\Delta I_D$ , which gives no information other than the magnitude of  $\Delta I_D$ . Other useful information was not expressed, e.g., the probability of obtaining either a certain value or interval of  $\Delta I_D$  and statistical parameters such as the mean and second moment. The model proposed in [34] is in terms of a probability density function of the normalized value of  $\Delta I_D$ . This is able to yield much useful information apart from the variance after applying a probability density function. However, only a FG-MOSFET operated in the saturation region has been considered while the short channel effects have been overlooked.

Hence, analytical probabilistic modelling of  $\Delta I_D$  for a single FGMOSFET was performed in this research. The results were generated using a probability density function of  $\Delta I_D/I_D$ . This was chosen as it is a convenient dimensionless quantity. Unlike previous work [34], both triode and saturation region operated FGMOSFET devices were considered and their short channel effects were taken into account. Therefore, this work is more complete, detailed and accurate that earlier studies. Compared to the model proposed in [33], which deals only with variances, the

Final manuscript received on April 2, 2017.

<sup>&</sup>lt;sup>1</sup> The author is with Faculty of Engineering and Graduated School of Information Technology, Siam University, Bangkok, Thailand., E-mail: rawid\_b@yahoo.com

<sup>&</sup>lt;sup>2</sup> The author is with School of Information Technology, Mea Fah Luang University, Chiangrai, Thailand., E-mail: ch.roungsan@gmail.com

resulting models of this work can give more useful information as it is in terms of probability density functions. Many useful statistical parameters and probabilities have been formulated using our model, emphasizing this point. The modelling process of this work has taken variations in the manufacturing process into account regarding a single FGMOSFET. Therefore, the resulting models are generic and can be extensively applied to any FGMOSFET associated circuit or system. These models are also very accurate. They can fit the probabilistic distributions of  $\Delta I_D/I_D$  for the candidate triode and saturation FG-MOSFETs of both N-type and P type devices obtained using Monte-Carlo SPICE simulations based on BSIM3v3 at a  $0.25\mu m$  level with high accuracy. In these cases, it was found that the saturation variation of a FGMOSFET is more severe than that of a triode device. They also satisfy the goodness of fit test at a 99% confidence level. As the formerly overlooked short channel effects have been now taken into account, our probabilistic model for a saturation FG-MOSFET is even more accurate than that proposed in [34].

With the statistical parameters and probabilities obtained by using our modelling results, the impact of  $\Delta I_D$  upon the design trade-offs associated with FGMOSFET devices can be studied and objective functions that support statistical/variability aware analysis and design can be formulated. It has also been mathematically shown that the occurrence of  $\Delta I_D$  is absolutely certain, which emphasizes the necessity of our work. Moreover, analytical probabilistic modelling and computationally efficient statistical/variability aware numerical analysis of FGMOSFET based circuits can be performed. In the subsequent section, an overview of FGMOSFET devices will be briefly given.

#### 2. PROBLEM OF CONVENTIONAL ONE-TAP MMSE-FDE FOR DFTS-OFDM SIG-NAL

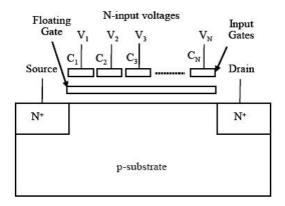

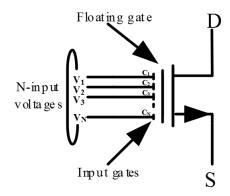

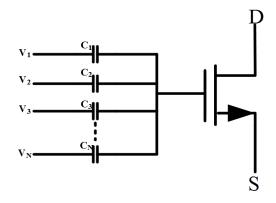

FGMOSFET is a special type of MOSFET device with an additional gate that is completely isolated within the oxide, namely a floating gate [11], [34]. A cross sectional view, symbol and equivalent circuit model of an N-type FGMOSFET with N inputs is depicted in Figs. 1-3 [11], [34]. If we let  $\{i\} = \{1, 2, 3, \ldots, N\}$ , it can be seen that Ci denotes the capacitance between any i<sup>th</sup> input and the floating gate. Moreover, the capacitive coupling ratio of any i<sup>th</sup> input  $(k_i)$  [2], [11], [34], can be defined as:

$$k_i = \frac{C_i}{\sum_{i=1}^{N} C_i} \tag{1}$$

Since  $I_D$  of the FGMOSFET in any region can be obtained by simply replacing the gate to source volt-

Fig.1: A cross sectional view of an N-type N inputs FGMOSFET [11], [34].

Fig.2: A symbol of an N-type N inputs FGMOSFET [34].

Fig.3: An equivalent circuit model of an N-type N inputs FGMOSFET [34].

age term in the drain current equation of an ordinary MOSFET device in that region with a floating gate to source voltage,  $V_{FGS}$  can be given by:

$$V_{FGS} = \sum_{i=1}^{N} k_i V_i - V_S \tag{2}$$

where  $V_i$  and  $V_S$  denote the voltage at any i<sup>th</sup> input of the FGMOSFET and the source terminal

voltage respectively.  $I_D$  of the triode and saturation region operated FGMOSFET with short channel effects taken into account can be respectively given as follows:

$$I_{D} = \mu C_{ox} \frac{W}{L} [1 - \theta (\sum_{i=1}^{N} k_{i} V_{i} - V_{S} - V_{t})]$$

$$\times [(\sum_{i=1}^{N} k_{i} V_{i} - V_{S} - V_{t}) V_{DS} - \frac{1}{2} V_{DS}^{2}]$$

(3)

$$I_{D} = \frac{\mu}{2} C_{ox} \frac{W}{L} [1 - \theta (\sum_{i=1}^{N} k_{i} V_{i} - V_{S} - V_{t})]$$

$$\times (\sum_{i=1}^{N} k_{i} V_{i} - V_{S} - V_{t})^{2} (1 + \lambda V_{DS})$$

$$(4)$$

where  $\mu$ ,  $\lambda$ ,  $\theta$ ,  $C_{ox}$ ,  $V_t$ , W and L represent the mobility of the carriers, channel length modulation coefficient, mobility degradation coefficient, gate oxide capacitance per unit area, threshold voltage, channel width and channel length, respectively. It is notable that the linearly approximated mobility degradation model [33] was used in the formulation of equations (3) and (4) for simplicity. In the subsequent section, our proposed analytical probabilistic modelling will be given.

### 3. THE ANALYTICAL PROBABILISTIC MODELING

Firstly,  $\Delta I_D/I_D$  must be defined. By taking the manufacturing process variations into account, random fluctuations in device level parameters, e.g.,  $\mu, V_t, W$  and L, among others, exist and cause fluctuation in the drain current. Thus  $\Delta I_D/I_D$  can be defined for any region of operation as:

$$\frac{\Delta I_D}{I_D} \stackrel{\Delta}{=} \frac{I_D - I_{D,ideal}}{I_{D,ideal}} \tag{5}$$

where  $I_{D,ideal}$  denotes the ideal drain current in which the physical level nonidealities have been neglected. In the following subsection, the analytical probabilistic modelling of a triode region FGMOS-FET is presented.

### 3.1 The modelling of triode region operated FGMOSFET

It should be noted here that intrinsic manufacturing process variations are emphasized as they are directly caused by the physical limits of the device [35]. These are intrinsic to the basic technology [36]. Moreover, the key intrinsic manufacturing process variations are random dopant fluctuation and line edge roughness [36]. These induce threshold voltage variations [35], [36]. As a result, such device level random

variations assume a Gaussian distribution and have been found to be dominant. Thus  $\Delta I_D/I_D$  of the FGMOSFET in the triode region can be analytically given using equations (3), (5) and the physical level parameters used by [37] are as follows:

$$\frac{\Delta I_D}{I_D} = \{\theta[1 - \theta(\sum_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1} - V_{DS}[(\sum_{i=1}^{N} k_i V_i - V_S - V_t)V_{DS} - \frac{1}{2}V_{DS}^2]^{-1}\} \times (V_t - qN_{sub}W_{dep}C_{inv}^{-1} - V_{FB} - 2\phi_F)$$

(6)

where  $C_{inv}$ ,  $N_{sub}$ ,  $V_{FB}$ ,  $W_{dep}$  and  $\phi_F$  denote capacitance of the inversion layer, substrate dopant concentration, flat band voltage, width of the depletion layer and the Fermi potential. These are physical level parameters. Moreover,  $V_t$  now randomly fluctuates.

For deriving the probability density function of  $\Delta I_D/I_D$  i.e.,  $f(\delta I_D/I_D)$ , where  $\delta I_D/I_D$  represents the corresponding sample variable, the often cited analytical model of device level random variation [37], [38] was adopted. As a result,  $f(\delta I_D/I_D)$  can be given by equation (6) and the adopted model is as follows:

$$\begin{split} f(\frac{\delta I_D}{I_D}) &= \sqrt{\frac{3WLC_{inv}^2 \{\theta[1-\theta(\sum\limits_{i=1}^N k_i V_i - V_S - V_t)]^{-1}}{\frac{-V_{DS}[(\sum\limits_{i=1}^N k_i V_i - V_S - V_t)V_{DS} - \frac{1}{2}V_{DS}^2]^{-1}\}^{-2}}{2\pi N_{sub}W_{dep}q^2}} \\ &= 3WLC_{inv}^2 \{\{\theta[1-\theta(\sum\limits_{i=1}^N k_i V_i - V_S - V_t)]^{-1} \\ &\times \exp[-\frac{-V_{DS}[(\sum\limits_{i=1}^N k_i V_i - V_S - V_t)V_{DS} - \frac{1}{2}V_{DS}^2]^{-1}\}^{-1}(\delta I_D/I_D)\}^2}{2N_{sub}W_{dep}q^2}] \end{split}$$

In the next subsection, the modelling of a FGMOS-FET device in the saturation region will be presented.

### 3.2 The modelling of saturation region operated FGMOSFET

For a FGMOSFET in the saturation region,  $\Delta I_D/I_D$  can be given in a similar manner to that of a FGMOSFET in the triode region, but using equation (4) as a basis instead of (3). Thus we obtain:

$$\frac{\Delta I_D}{I_D} = \{\theta[1 - \theta(\sum_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1} - 2(\sum_{i=1}^{N} k_i V_i - V_S - V_t)^{-1}\} \times (V_t - q N_{sub} W_{dep} C_{inv}^{-1} - V_{FB} - 2\phi_F)$$

(8)

As a result,  $f(\delta I_D/I_D)$  of the saturation FGMOS-FET can be given by equation (8) and a similar approach to that of the triode FGMOSFET as follows:

$$f(\frac{\delta I_D}{I_D}) = \sqrt{\frac{3WLC_{inv}^2 \{\theta [1 - \theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t]]^{-1} - 2(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)^{-1}\}^2}{\frac{2\pi N_{sub} W_{dep} q^2}{(9)}}$$

$$\begin{split} &3WLC_{inv}^{2}\{\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}\\ &\times\exp[-\frac{-2(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})^{-1}\}^{-1}(\delta I_{D}/I_{D})\}^{2}}{2N_{sub}W_{dev}q^{2}}] \end{split}$$

Since the short channel effects have now been considered, the resulting  $f(\delta I_D/I_D)$  of the saturation FGMOSFET is more detailed and thus more accurate than that proposed in [34]. This will be shown in the subsequent section where verification of our analytical modelling results is presented.

#### 4. VERIFICATION OF THE MODELING RESULTS

As a comparison to [34], our verification was performed based on the 0.25  $\mu{\rm m}$  level CMOS process technology of TSMC. For simplicity, the candidate FGMOSFET was chosen from two inputs types. It should be noted that the modelling of a FGMOSFET for simulation was done based on the equivalent FGMOSFET circuit in Fig. 3. Modelling of the core MOSFET was achieved using BSIM3v3. The simulation methodology proposed in [39] was adopted for solving the convergence problem. The necessary parameters were extracted by MOSIS. A nominal L of 0.25  $\mu{\rm m}$  along with a nominal W/L of 20/0.25 was chosen. Of course, both NMOS and PMOS technological bases were considered.

Similar to [34], verification was performed in both qualitative and quantitative aspects. In the qualitative sense, graphical plots of  $f(\delta I_D/I_D)$  of triode and saturation FGMOSFETs, which are the results of the analytical probabilistic modelling, were compared to those of the candidate triode and saturation FG-MOSFETs based upon the probability distribution of  $\Delta I_D/I_D$ , and  $f'(\delta I_D/I_D)$  obtained from Monte-Carlo SPICE simulations with 3000 runs. Concerning the quantitative aspects, the Kolmogorov-Smirnof test, i.e., the KS-test, is a powerful goodness of fit measure [40], [41] that was used with a 99% confidence level. According to [40] and [41], the objective of the KS-test is to perform a comparison of the KS-test statistic, KS and the critical value, c, where it can be stated that any model can accurately fit its target data set if and only if  $KS \leq c$ . For this research, KS can be defined as:

$$KS = \max_{\delta I_D/I_D} [|F'(\frac{\delta I_D}{I_D})| - |F(\frac{\delta I_D}{I_D})|] \qquad (10)$$

where,

$$F(\frac{\delta I_D}{I_D}) = \int_{-\infty}^{\delta I_D/I_D} f(x)dx \tag{11}$$

$$F'(\frac{\delta I_D}{I_D}) = \int_{-\infty}^{\delta I_D/I_D} f'(x)dx \tag{12}$$

Since the confidence level of the test was 99%, c can be given by equation [41]:

$$c = \frac{1.63}{\sqrt{n}} \tag{13}$$

where n denotes the number of runs for the Monte-Carlo SPICE analysis, i.e., 3000, as previously stated. Thus, c=0.0297596. In the upcoming subsections, verification of the triode and saturation FGMOSFET based modelling results will be given.

### 4.1 Verification of the triode FGMOSFET based result

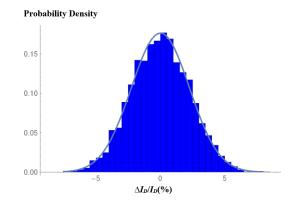

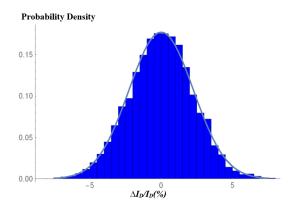

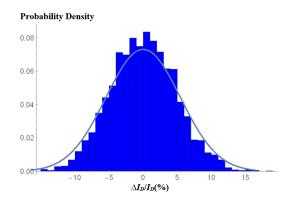

The graphical comparisons of  $f(\delta I_D/I_D)$  for the triode region FGMOSFET given by equation (7) with N=2 as a candidate FGMOSFET, has two inputs.  $f'(\delta I_D/I_D)$  obtained using the candidate triode region FGMOSFET is depicted in Fig. 4 and Fig. 5 for and N type and P-type FGMOSFETs, respectively, where  $\Delta I_D/I_D$  is dimensionless and is expressed as a percentage. It can be seen that there is strong agreement between  $f(\delta I_D/I_D)$  values obtained from the analytical probabilistic modelling and  $f'(\delta I_D/I_D)$  obtained from the candidate FGMOSFET.

Moreover, it can be seen that the resulting KS obtained using equation (7) with N=2 for determining can be found as KS=0.01935 and KS=0.01873 for N type and P-type FGMOSFETs, respectively. Both were lower than c=0.0297596, which means that our derived  $f(\delta I_D/I_D)$  of the FGMOSFET in the triode region can fit the candidate triode FGMOSFET based data with 99% confidence. These KS-test results and the aforementioned strong agreement in the comparative plots verify the accuracy of our triode region analytical probabilistic modelling.

**Fig.4:** N-type triode FGMOSFET based comparative plots of  $f(\delta I_D/I_D)$  (line) and  $f'(\delta I_D/I_D)$  (histogram).

#### 4.2 Verification of the saturation FGMOS-FET based result

For the FGMOSFET in saturation, the comparative plots of  $f(\delta I_D/I_D)$  given by equation (9) with

**Fig.5:** P-type triode FGMOSFET based comparative plots of  $f(\delta I_D/I_D)$  (line) and  $f'(\delta I_D/I_D)$  (histogram).

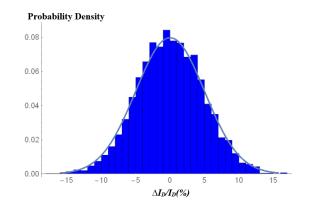

N=2 and  $f'(\delta I_D I_D)$  obtained using the candidate saturation FGMOSFET are depicted in Figs. 6 and 7 for N-type and P-type devices, respectively, where  $\Delta I_D/I_D$  is expressed as a percentage. From these figures, strong agreement between  $f(\delta I_D/I_D)$  and  $f'(\delta I_D/I_D)$  can be observed. Moreover, it has been found that that the variation of the saturation FGMOSFET was more severe than that of the device in the triode region as indicated by the more dispersed distributions of  $\Delta I_D/I_D$  of the saturation FGMOSFET.

Using equation (9) with N = 2 for determining  $F(\delta I_D/I_D)$ , the resulting KS values for N-type and P-type FGMOSFETs were found to be KS = 0.02013and KS = 0.01895, respectively, which are both lower than c = 0.0297596. This means that our derived  $f(\delta I_D/I_D)$  of the saturation FGMOSFET can fit the candidate saturation FGMOSFET based data with 99% confidence. The strong agreement in the comparative plots and the KS-test results verify the accuracy of our saturation region analytical probabilistic modelling. Since the above KS values are lower than those of previous modelling results [34], where KS = 0.02823 and KS = 0.02619 for N-type and Ptype FGMOSFETs, respectively, it can be seen that our saturation region modelling results are more accurate.

#### 5. THE APPLICATIONS

Unlike the previous variance term models [33], many statistical parameters and probabilities associated with  $\Delta I_D$  can be formulated for both the triode and saturation region operated FGMOSFETs using our modelling results. This is because they are in terms of probability density functions. With these parameters and probabilities, it has been mathematically shown that the occurrence of  $\Delta I_D$  is absolutely certain, the impact of  $\Delta I_D$  to the design trade-offs associated with FGMOSFET can be studied and objective functions conducive to statistical/variability

**Fig.6:** N-type saturation FGMOSFET based comparative plots of  $f(\delta I_D/I_D)$  (line) and  $f'(\delta I_D/I_D)$  (histogram).

Fig.7: P-type saturation FGMOSFET based comparative plots of  $f(\delta I_D/I_D)$  (line) and  $f'(\delta I_D/I_D)$  (histogram).

aware analysis and design can be obtained. Moreover, analytical probabilistic modelling and computationally efficient statistical/variability aware numerical simulation of the FGMOSFET based circuits can also be performed. These applications of our modelling results will be subsequently presented in this section.

### 5.1 Formulation of statistical parameters and the related objective functions

Using our  $f(\delta I_D/I_D)$ , statistical parameters of  $\Delta I_D/I_D$  such as average, median and variance can be analytically obtained for FGMOSFETs in both the triode and saturation regions. To do so, conventional statistical mathematics must be applied. For example, the average of  $\Delta I_D/I_D$  i.e.  $\overline{\Delta I_D/I_D}$ , i.e., its first moment, can be mathematically defined as:

$$\frac{\overline{\Delta I_D}}{I_D} = \int_{-\infty}^{\infty} \frac{\delta I_D}{I_D} f(\frac{\delta I_D}{I_D}) d\frac{\delta I_D}{I_D}$$

(14)

After applying our  $f(\delta I_D/I_D)$  given by equations (7) and (9) for triode and saturation FGMOSFETs,

to equation (14),  $\overline{\Delta I_D/I_D}$  was found to be zero for FGMOSFETs in both the triode and saturation regions.

Moreover, the median value of  $\Delta I_D/I_D$ , m can be determined by solving the following equation:

$$\int_{-\infty}^{\infty} f(\frac{\delta I_D}{I_D}) d\frac{\delta I_D}{I_D} = \frac{1}{2}$$

(15)

After applying equations (7) and (9), it was found that m = 0 for the FGMOSFET in both regions.

Even though  $\overline{\Delta I_D/I_D}$  and m were found to be zero, the variance of  $\Delta I_D/I_D$   $\sigma^2_{\Delta I_D/I_D}$  was not. The value of  $\sigma^2_{\Delta I_D/I_D}$  can be mathematically defined as:

$$\sigma_{\frac{\Delta I_D}{I_D}}^2 = \int_{-\infty}^{\infty} \left(\frac{\delta I_D}{I_D} - \frac{\overline{\Delta I_D}}{I_D}\right)^2 f(\frac{\delta I_D}{I_D}) d\frac{\delta I_D}{I_D} \quad (16)$$

By applying equations (7) and (9),  $\sigma^2_{\Delta I_D/I_D}$  of the FGMOSFET in the triode and saturation regions can be respectively determined as:

$$\sigma_{\frac{\Delta I_D}{I_D}}^2 = \frac{N_{sub} W_{dep} q^2}{3W L C_{inv}^2 \{ \theta [1 - \theta (\sum_{i=1}^N k_i V_i - V_S - V_t)]^{-1}}$$

(17)

$$-V_{DS}[(\sum\limits_{i=1}^{N}k_{i}V_{i}\!-\!V_{S}\!-\!V_{t})V_{DS}\!-\!\frac{1}{2}V_{DS}^{2}]^{-1}\}^{-2}$$

$$\sigma_{\frac{\Delta I_D}{I_D}}^2 = \frac{N_{sub} W_{dep} q^2}{3W L C_{inv}^2 \{\theta [1 - \theta (\sum_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1}}$$

(18)

$$-2(\sum_{i=1}^{N} k_i V_i - V_S - V_t)^{-1}$$

Since  $\overline{\Delta I_D/I_D}=0$ , the second moment of  $\Delta I_D/I_D$ ,  $\overline{(\Delta I_D/I_D)^2}$  is mathematically defined as:

$$\overline{(\frac{\Delta I_D}{I_D})^2} = \int_{-\infty}^{\infty} (\frac{\delta I_D}{I_D})^2 f(\frac{\delta I_D}{I_D}) d\frac{I_D}{I_D}$$

(19)

and was been found to be equal to  $\sigma_{\Delta I_D/I_D}^2$ . Thus  $\overline{(\Delta I_D/I_D)^2}$  can also be given by equations (17) and (18) for triode and saturation FGMOSFETs, respectively.

Finally, the moment generating function of  $\Delta I_D/I_D$ , M(u), is the summation of all moments of  $\Delta I_D/I_D$  including the first and second ones [42]. It is mathematically defined as:

$$M(u) = \int_{-\infty}^{\infty} \exp(u\frac{\delta I_D}{I_D}) f(\frac{\delta I_D}{I_D}) d\frac{I_D}{I_D}$$

(20)

These can be respectively obtained for triode and saturation FGMOSFETs by applying equations (7)

and (9) to (20) as follows:

$$M(u) = \exp\left[\frac{N_{sub}W_{dep}q^2}{6WLC_{inv}^2\{\theta[1-\theta(\sum_{i=1}^{N}k_iV_i-V_S-V_t)]^{-1}}\right]$$

(21)

$$-V_{DS}[(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})V_{DS}-\frac{1}{2}V_{DS}^{2}]^{-1}\}^{-2}$$

$$M(u) = \exp\left[\frac{N_{sub}W_{dep}q^{2}u^{2}}{6WLC_{inv}^{2}\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}}\right]$$

(22)

$$-2(\sum_{i=1}^{N} k_i V_i - V_S - V_t)^{-1}\}^{-2}$$

From equations (17) and (18), it can be seen that:

$$\sigma_{\Delta I_D/I_D}^2 \alpha \frac{1}{WL} \tag{23}$$

for both the triode and saturation region operated FGMOSFETs. Thus, lowering the device area causes an increased  $\Delta I_D$  as a penalty. This is an example of the impact of  $\Delta I_D$  upon the design trade-offs involving FGMOSFETs. Using equationss (17) and (18), the minimum value of WL,  $(WL)_{min}$  which dictates the minimum area of the transistor, can be obtained for the triode and saturation FGMOSFETs as follows:

$$N_{Sub}W_{dep}q^{2}\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})^{-1}]$$

$$(WL)_{\min} = \frac{-V_{DS}[(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})V_{DS}-\frac{1}{2}V_{DS}^{2}]^{-1}\}^{-2}}{3C_{inv}^{2}\sigma_{\Delta I_{D}}^{2}/I_{D,\max}}$$

(24)

$$N_{sub}W_{dep}q^2\{\theta[1\!-\!\theta(\sum\limits_{i=1}^{N}k_iV_i\!-\!V_S\!-\!V_t)^{-1}]$$

$$(WL)_{\min} = \frac{-2(\sum_{i=1}^{N} k_i V_i - V_S - V_t)^{-1}\}^{-2}}{\frac{3WLC_{inv}^2 \sigma_{\Delta I_D/I_D, \max}^2}{2}}$$

(25)

where  $\sigma^2_{\Delta I_D/I_{D, {

m max}}}$  denotes the maximum acceptable value of  $\sigma^2_{\Delta I_D/I_D}.$

Since  $\sigma_{\Delta I_D/I_D}^2$  reflects the size of  $\Delta I_D/I_D$ , the statistical/variability aware design of any single FG-MOSFET can be performed using the optimization scheme with the following objective function:

$$\min[\sigma_{\Delta I_D/I_D}^2] \tag{26}$$

where either equation (17) or (18) must be used according to the operating region of the FGMOSFET under consideration.

### 5.2 The formulation of the useful probabilities and objective functions

In order to do so, the cumulative distribution function of  $\Delta I_D/I_D$ ,  $F(\delta I_D/I_D)$  and the survival function [43] of  $\Delta I_D/I_D$ ,  $S(\delta I_D/I_D)$  must first be derived. It can be seen that  $F(\delta I_D/I_D)$  is equivalent to the probability that  $\Delta I_D/I_D \leq \delta I_D/I_D$  i.e.,

$\Pr\{\Delta I_D/I_D \leq \delta I_D/I_D\}$ . This is also necessary for determining KS as shown in the previous section, and can be obtained using our  $f(\delta I_D/I_D)$  as in equation (11). For a FGMOSFET in the triode and saturation regions with an arbitrary value of N,  $F(\delta I_D/I_D)$  can be respectively given by applying equations (7) and (9) to (11) without specifying N as follows:

$$\begin{split} F(\frac{\delta I_{D}}{I_{D}}) &= \frac{1}{2} [1 + erf(\frac{\sqrt{3WL}C_{inv}(\delta I_{D}/I_{D})}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1 - \theta(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})]^{-1}})] \\ &- V_{DS}[(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})V_{DS} - \frac{1}{2}V_{DS}^{2}]^{-1}\} \end{split}$$

$$\begin{split} F(\frac{\delta I_{D}}{I_{D}}) &= \frac{1}{2} [1 + erf(\frac{\sqrt{3WLC}_{inv}(\delta I_{D}/I_{D})}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1 - \theta(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})]^{-1}})]} \\ &- 2(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})^{-1}\} \end{split}$$

where  $\operatorname{erf}()$  denotes the error function and can be mathematically defined in terms of an arbitrary variable, y, as:

$$erf(y) = \frac{2}{\sqrt{\pi}} \int_0^y \exp(-u^{2)du}$$

(29)

Alternatively,  $S(\delta I_D/I_D)$ , which is equivalent to the probability that  $\Delta I_D/I_D > \delta I_D/I_D$ , i.e.,  $\Pr\{\Delta I_D/I_D > \delta I_D/I_D\}$ , can be mathematically defined as:

$$S(\frac{\delta I_D}{I_D}) = \int_{\delta I_D/I_D}^{\infty} f(x)dx \tag{30}$$

Thus,  $S(\delta I_D/I_D)$  of a FGMOSFET in the triode and saturation regions can be found by respectively applying equations (7) and (9) to (30) as given by equations (31) and (32). Then, the useful probabilities and objective functions can be derived and used for statistical/variability aware analysis and design involving FGMOSFETs:

$$\begin{split} S(\frac{\delta I_{D}}{I_{D}}) = & 1 - \frac{1}{2} [1 + erf(\frac{\sqrt{3WL}C_{inv}(\delta I_{D}/I_{D})}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1 - \theta(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})]^{-1}})] \\ & - V_{DS}[(\sum\limits_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})V_{DS} - \frac{1}{2}V_{DS}^{2}]^{-1}\} \end{split}$$

$$S(\frac{\delta I_{D}}{I_{D}}) = 1 - \frac{1}{2} \left[ 1 + erf\left(\frac{\sqrt{3WLC}_{inv}(\delta I_{D}/I_{D})}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1 - \theta(\sum_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})]^{-1}}\right) \right]$$

$$-2(\sum_{i=1}^{N}k_{i}V_{i} - V_{S} - V_{t})^{-1}\}$$

(32)

Firstly, it will be shown that the probability that  $\Delta I_D/I_D$ , which is a continuous random variable, lies

within a certain range given as [a, b] and can be derived using  $F(\delta I_D/I_D)$ . This probability is denoted as  $\Pr\{a \leq \Delta I_D/I_D \leq b\}$ , and can be given in terms of  $F(\delta I_D/I_D)$  as:

$$\Pr\{a \le \frac{\Delta I_D}{I_D} \le b\} = F(b) - F(a) \tag{33}$$

Thus, by applying equations (27) and (28) to (33),  $\Pr\{a \leq I_D/I_D \leq b\}$  of a FGMOSFET in the triode and saturation regions can be respectively obtained as follows:

$$\begin{split} \Pr\{a \leq & \frac{\Delta I_D}{I_D} \leq b\} = \frac{1}{2} \left[ erf(\frac{\sqrt{3WL}C_{inv}b}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)]^{-1}}) - (34) - V_{DS}[(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)V_{DS} - \frac{1}{2}V_{DS}^2]^{-1}\} \\ & - erf(\frac{\sqrt{3WL}C_{inv}a}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)]^{-1}})] \\ & - V_{DS}[(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)V_{DS} - \frac{1}{2}V_{DS}^2]^{-1}\} \end{split}$$

$$\begin{split} \Pr\{a \leq & \frac{\Delta I_D}{I_D} \leq b\} = \frac{1}{2} \left[ erf(\frac{\sqrt{3WLC_{inv}b}}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)]^{-1}}) \right. \\ & \left. \qquad \qquad (35) \\ & -2(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)^{-1} \right\} \\ & -erf(\frac{\sqrt{3WLC_{inv}a}}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)]^{-1}})] \\ & -2(\sum\limits_{i=1}^{N}k_iV_i-V_S-V_t)^{-1} \} \end{split}$$

It can be seen that  $\Pr\{a \leq \Delta I_D/I_D \leq b\}$  can be directly used for predicting the probability that  $\Delta I_D/I_D$  lies within an arbitrary predetermined range. Moreover, the probability that the magnitude of  $\Delta I_D/I_D$  does not exceed the allowable maximum value, which the resulting variation in the performance of FGMOSFET, can be determined using  $\Pr\{a \leq \Delta I_D/I_D \leq b\}$ . This probability is obviously useful in statistical/variability aware analysis and design involving FGMOSFETs.

To do so, we let the aforesaid maximum value be  $|\Delta I_D/I_D|_{\rm max}$ . Thus such probability denoted by  $\Pr\{|\Delta I_D/I_D| \leq |\Delta I_D/I_D|_{\rm max}\}$ , can be determined using  $\Pr\{a \leq \Delta I_D/I_D \leq b\}$  with  $a = -|\Delta I_D/I_D|_{\rm max}$  and  $b = |\Delta I_D/I_D|_{\rm max}$ . This is because  $|\Delta I_D/I_D| \leq |\Delta I_D/I_D|_{\rm max}$  is equivalent to  $-|\Delta I_D/I_D|_{\rm max} \leq \Delta I_D/I_D \leq |\Delta I_D/I_D|_{\rm max}$ . As a result,  $\Pr\{|\Delta I_D/I_D| \leq |\Delta I_D/I_D|_{\rm max}\}$  of the triode and saturation FGMOSFETs can be obtained using equations (34) and (35) as follows:

$$\Pr\{\left|\frac{\Delta I_D}{I_D}\right| \leq \left|\frac{\Delta I_D}{I_D}\right|_{\max}\} = \frac{1}{2} \left[ erf(\frac{\sqrt{3WL}C_{inv} |\Delta I_D/I_D|_{\max}}{\sqrt{2N_{sub}W_{dep}} q \{\theta [1-\theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1}}) \right]$$

$$(36)$$

$$\begin{split} -V_{DS}[(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})V_{DS}-\frac{1}{2}V_{DS}^{2}]^{-1}\}\\ -erf(\frac{\sqrt{3WL}C_{inv}|\Delta I_{D}/I_{D}|_{\max}}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum\limits_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}})]\\ -V_{DS}[(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})V_{DS}-\frac{1}{2}V_{DS}^{2}]^{-1}\} \end{split}$$

$$\begin{split} \Pr\{ \left| \frac{\Delta I_{D}}{I_{D}} \right| \leq & \left| \frac{\Delta I_{D}}{I_{D}} \right|_{\max} \} = \frac{1}{2} \left[ erf(\frac{\sqrt{3WLC}_{inv} | \Delta I_{D}/I_{D} | \max}{\sqrt{2N_{sub}W_{dep}} q \{\theta \| - \theta(\sum\limits_{i=1}^{N} k_{i}V_{i} - V_{S} - V_{t}) \|^{-1}} \right] \\ & - 2(\sum\limits_{i=1}^{N} k_{i}V_{i} - V_{S} - V_{t})^{-1} \}^{-2} \\ & - erf(\frac{\sqrt{3WLC}_{inv} | \Delta I_{D}/I_{D} | \max}{\sqrt{2N_{sub}W_{dep}} q \{\theta \| - \theta(\sum\limits_{i=1}^{N} k_{i}V_{i} - V_{S} - V_{t}) \|^{-1}} )] \\ & - 2(\sum\limits_{i=1}^{N} k_{i}V_{i} - V_{S} - V_{t})^{-1} \}^{-2} \end{split}$$

Since maximizing  $\Pr\{|\Delta I_D/I_D| \leq |\Delta I_D/I_D|_{\max}\}$  yields the greatest likelihood of obtaining an acceptable magnitude of  $\Delta I_D/I_D$ , which is a goal of the statistical/variability aware design, the following objective function was found useful:

$$\max[\Pr\{|\Delta I_D/I_D| \le |\Delta I_D/I_D|_{\max}\}] \tag{38}$$

From equations (36) and (37), it can be seen that (38) can be satisfied for a FGMOSFET in both operating regions using the optimum values of controllable parameters, such as W, L and  $V_S$ .

Contrary to  $\Pr\{a \leq \Delta I_D/I_D \leq b\}$ , the probability that  $\Delta I_D/I_D$  lies outside [a, b] i.e.,  $\Pr\{(\Delta I_D/I_D < a) \vee (\Delta I_D/I_D < b)\}$ , can be obtained using  $S(\delta I_D/I_D)$  as:

$$\Pr\{\left(\frac{\Delta I_D}{I_D} < a\right) \lor \left(\frac{\Delta I_D}{I_D} < b\right)\} = 1 + S(b) - S(a) (39)$$

Thus, applying equations (31) and (32) to (39),  $\Pr\{(\Delta I_D/I_D < a) \lor (\Delta I_D/I_D < b)\}$  of the triode and saturation FGMOSFETs can be respectively given by equationss (40) and (41). Using  $\Pr\{(\Delta I_D/I_D < a) \lor (\Delta I_D/I_D < b)\}$  with  $a = -|\Delta I_D/I_D|_{\max}$  and  $b = |\Delta I_D/I_D|_{\max}$ , the probability that  $|\Delta I_D/I_D| > |\Delta I_D/I_D|_{\max}$ , can be obtained. This is because  $|\Delta I_D/I_D| > |\Delta I_D/I_D|_{\max}$ , is equivalent to the union of  $\Delta I_D/I_D < -|\Delta I_D/I_D|_{\max}$  and  $\Delta I_D/I_D > |\Delta I_D/I_D|_{\max}$ , which are mutually exclusive events.

$$\begin{split} \Pr\{ (\frac{\Delta I_D}{I_D} \!<\! a) \lor (\frac{\Delta I_D}{I_D} \!<\! b) \} \\ = & 1 \!-\! \tfrac{1}{2} [\!erf(\!\frac{\sqrt{3WL}C_{inv}\,b}{\sqrt{2N_{sub}W_{dep}}q_{\{\theta[1\!-\!\theta(\sum\limits_{i=1}^{N}k_iV_i\!-\!V_S\!-\!V_t)]\!-\!1}}) \\ & - V_{DS}[(\sum\limits_{i=1}^{N}k_iV_i\!-\!V_S\!-\!V_t)V_{DS}\!-\! \tfrac{1}{2}V_{DS}^2]^{-1} \} \end{split}$$

$$-erf(\frac{\sqrt{3WL}C_{inv}a}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}})]$$

$$-V_{DS}[(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})V_{DS}-\frac{1}{2}V_{DS}^{2}]^{-1}\}$$

(40)

$$\begin{split} \Pr\{ & (\frac{\Delta I_D}{I_D} < a) \lor (\frac{\Delta I_D}{I_D} > b) \} = 1 - \frac{1}{2} \left[ erf(\frac{\sqrt{3WLC}_{inv}b}{\sqrt{2N_{sub}W_{dep}} q \{\theta [1 - \theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t])^{-1}}) \right] \\ & \qquad \qquad (41) \\ & \qquad \qquad - 2 (\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)^{-1} \} \\ & \qquad \qquad - erf(\frac{\sqrt{3WLC}_{inv}a}{\sqrt{2N_{sub}W_{dep}} q \{\theta [1 - \theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1}})] \\ & \qquad \qquad - 2 (\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)^{-1} \} \end{split}$$

Therefore,  $\Pr\{|\Delta I_D/I_D| > |\Delta I_D/I_D|_{\max}\}$  of the triode and saturation FGMOSFETs can be given using equations (38) and (39) as follows:

$$\Pr\{\left|\frac{\Delta I_{D}}{I_{D}}\right| > \left|\frac{\Delta I_{D}}{I_{D}}\right|_{\max}\} \\

= 1 - \frac{1}{2} \left\{ rf\left(\frac{\sqrt{3WL}C_{inv}|\Delta I_{D}/I_{D}|_{\max}}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}}\right) \\

-V_{DS}\left[\left(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t}\right)V_{DS} - \frac{1}{2}V_{DS}^{2}\right]^{-1}\} \\

-erf\left(\frac{\sqrt{3WL}C_{inv}|\Delta I_{D}/I_{D}|_{\max}}{\sqrt{2N_{sub}W_{dep}}q\{\theta[1-\theta(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t})]^{-1}}\right)] \\

-V_{DS}\left[\left(\sum_{i=1}^{N}k_{i}V_{i}-V_{S}-V_{t}\right)V_{DS} - \frac{1}{2}V_{DS}^{2}\right]^{-1}\} \tag{42}$$

$$\begin{split} \Pr\{ & \frac{|\Delta I_D|}{I_D} | \leq \frac{|\Delta I_D|}{I_D} \Big|_{\max} \} = 1 - \frac{1}{2} [ erf( \frac{\sqrt{3WLC_{inv}} |\Delta I_D/I_D|_{\max}}{\sqrt{2N_{sub}W_{dep}} q \{\theta \| - \theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t) \|^{-1}}) ] \\ & \qquad \qquad (43) \\ & \qquad \qquad - 2(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)^{-1} \}^{-2} \\ & \qquad \qquad - erf( \frac{\sqrt{3WLC_{inv}} |\Delta I_D/I_D|_{\max}}{\sqrt{2N_{sub}W_{dep}} q \{\theta [1 - \theta(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)]^{-1}}) ] \\ & \qquad \qquad - 2(\sum\limits_{i=1}^{N} k_i V_i - V_S - V_t)^{-1} \}^{-2} \end{split}$$

The greatest probability of obtaining an acceptable magnitude of  $\Delta I_D/I_D$  can be alternatively determined by minimizing  $\Pr\{|\Delta I_D/I_D|>|\Delta I_D/I_D|_{\max}\}$ . So, the following objective function can also be satisfied for both the triode and saturation FGMOSFETs using the optimum settings of controllable parameters. The following has been found useful:

$$\min[\Pr\{|\Delta I_D/I_D| > |\Delta I_D/I_D|_{\max}\}] \qquad (44)$$

Finally, the probability of the occurrence of  $\Delta I_D$  will be determined. Since the occurrence of  $\Delta I_D$  yields  $|\Delta I_D/I_D| > 0$ , this probability is equal to the probability that  $|\Delta I_D/I_D| > 0$  i.e.,  $\Pr{\Delta I_D/I_D} > 0$ }. As  $|\Delta I_D/I_D| > 0$  is equivalent to the union of  $\Delta I_D/I_D < 0$  and  $\Delta I_D/I_D < 0$ , which are mutually

exclusive events,  $\Pr\{|\Delta I_D/I_D| > 0\}$  can be determined using with a = b = 0. As a result, it was found by using equations (40) and (41) with a = b = 0, that  $\Pr\{\Delta I_D/I_D > 0\} = 1$  for both the triode and saturation FGMOSFETs. This means that the probability of the occurrence of  $\Delta I_D$  is equal to 1 for a FGMOSFET in both operating regions. Thus, the occurrence of  $\Delta I_D$  is absolutely certain. This emphasizes the necessity of our work and focuses on the certainly of  $\Delta I_D$ .

### 5.3 Analytical probabilistic modelling of the FGMOSFET based circuit

Using our  $f(\delta I_D/I_D)$ , the analytical probabilistic modelling of a FGMOSFET based circuit is possible. This is because the key parameter of such a circuit depends upon the  $I_D$  values intrinsic to this FGMOSFET. Here, we let this parameter and its variation be respectively represented as X and  $\Delta X$ . Thus, the analytical probabilistic modelling of a FGMOSFET based circuit can be conveniently performed by determining the probability density function of the normalized value of  $\Delta X$  with respected to X,  $\Delta X/X$ , i.e.,  $g(\Delta X/X)$ , where  $\delta X/X$  is the sample variable of  $\Delta X/X$ . To obtain  $g(\Delta X/X)$ , the principle of transformation of random variables [42] must be applied. If we assume that a single FGMOSFET in the circuit affects X,  $g(\Delta X/X)$  can be given as [34]:

$$g(\frac{\delta X}{X}) = f(\frac{\delta I_D}{I_D}(\frac{\delta X}{X})) \left[ \left\| \frac{\partial (\delta I_D/I_D)}{\partial (\delta X/X)} \right\|_{\frac{\delta I_D}{I_D} \to \frac{\delta I_D}{I_D}(\frac{\delta X}{X})} \right]^{-1}$$

$$\tag{45}$$

With the resulting  $g(\delta X/X)$ , the statistical parameters of  $\Delta X/X$  and probabilities needed for statistical/variability aware design can be analytically determined in a similar manner to those of  $\Delta I_D/I_D$ . Thus, for example, the mean, variance, second moment of  $\Delta X/X$  and the probability that the magnitude of  $\Delta X/X$  does not exceed its maximum allowable value,  $|\Delta X/X|_{\rm max}$ , can be respectively given using the following equations:

$$\frac{\overline{\Delta X}}{X} = \int_{-\infty}^{\infty} \frac{\delta X}{X} f(\frac{\delta X}{X}) d\frac{\delta X}{X}$$

(46)

$$\sigma_{\frac{\Delta X}{X}}^{2} = \int_{-\infty}^{\infty} \left(\frac{\delta X}{X} - \frac{\overline{\delta X}}{X}\right)^{2} f(\frac{\delta X}{X}) d\frac{\delta X}{X}$$

(47)

$$\overline{(\frac{\Delta X}{X})^2} = \int_{-\infty}^{\infty} (\frac{\delta X}{X})^2 f(\frac{\delta X}{X}) d(\frac{\delta X}{X}) \tag{48}$$

$$\Pr\left\{\left|\frac{\Delta X}{X}\right| \le \left|\frac{\Delta X}{X}\right|_{\max}\right\} = G\left(\left|\frac{\Delta X}{X}\right|_{\max}\right) - G\left(-\left|\frac{\Delta X}{X}\right|_{\max}\right) \tag{49}$$

where  $G(|\Delta X/X|_{\text{max}})$  and  $G(-|\Delta X/X|_{\text{max}})$  are respectively the cumulative distribution function of  $\Delta X/X$  denoted by  $G(\delta X/X)$  with  $\delta X/X = |\Delta X/X|_{\text{max}}$  and  $\delta X/X = -|\Delta X/X|_{\text{max}} \cdot G(\delta X/X)$  can be generally given by:

$$G(\frac{\delta X}{X}) = \int_{-\infty}^{\delta X/X} g(x)dx \tag{50}$$

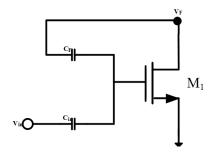

As a case study using a practical FGMOSFET based circuit, we let X be the transconductance,  $G_m$ , of a FGMOSFET based voltage to current converter (VIC) [44]. The core circuit of this VIC is depicted in Fig. 8 [34], where M1 is a FGMOSFET and has been drawn in its equivalent circuit form.

Since M1, which operates in the saturation region, affects the performance of this FGMOSFET based VIC,  $G_m$  is equal to the transconductance of M1 and can be given in term its  $I_D$  value, i.e.,  $I_{D1}$ , by equation (51). It can be seen that  $C_f$  and  $C_{in}$ , which act as the feedback and input capacitances, are actually the coupling capacitances of M1. As this FGMOSFET has two inputs and its source terminal has been grounded,  $I_{D1}$  can be given in terms of  $C_f$  and  $C_{in}$  by equation (52). Thus, the normalized random variation in  $G_m$ ,  $\Delta G_m/G_m$ , can be formulated in terms of  $\Delta I_{D1}/I_{D1}$  as given by equation (53). It should be noted that the short channel effects have been taken into account in the formulation of these equations.

Fig.8: The core circuit of FGMOSFET based VIC [34].

$$G_{m} = \frac{C_{in}}{C_{in} + C_{f}} \left\{ 2 \left( \frac{C_{in}V_{in}}{C_{in} + C_{f}} + \frac{C_{f}V_{f}}{C_{in} + C_{f}} - V_{t} \right)^{-1} - \theta \left[ 1 - \theta \left( \frac{C_{in}V_{in}}{C_{in} + C_{f}} + \frac{C_{f}V_{f}}{C_{in} + C_{f}} - V_{t} \right) \right]^{-1} \right\} I_{D1}$$

(51)

$$I_{D1} = \frac{\mu}{2} C_{ox} \frac{W}{L} \left[ 1 - \theta \left( \frac{C_{in} V_{in}}{C_{in} + C_f} + \frac{C_f V_f}{C_{in} + C_f} - V_t \right) \right] \times \left( \frac{C_{in} V_{in}}{C_{in} + C_f} + \frac{C_f V_f}{C_{in} + C_f} - V_t \right)^2 (1 + \lambda V_{DS})$$

(52)

$$\frac{\Delta G_m}{G_m} = \frac{\Delta I_{D1}}{I_{D1}} \tag{53}$$

As a result, the probability density function of  $\Delta G_m/G_m$ ,  $g(\delta G_m/G_m)$  can be analytically determined using our  $f(\delta I_D/I_D)$  derived of the saturation FGMOSFET, i.e., equations (9), with N =(2, (45)) and (53) as given by equation (54), where  $\delta G_m/G_m$  is the sample variance of  $\Delta G_m/G_m$ . Using  $g(\delta G_m/G_m)$ , the useful statistical parameters of  $\Delta G_m/G_m$  and probabilities can be analytically obtained. As an example, the variance of  $\Delta G_m/G_m$ ,  $\sigma^2_{\Delta G_m/G_m}$ , which was analytically determined using equation (47) with  $\Delta G_m/G_m$  and  $g(\delta G_m/G_m)$ , serve as  $\Delta X/X$  and  $g(\delta X/X)$ , respectively, in this practical case study. They can be obtained as given by equation (55). Similar to equations (51)-(55), the short channel effects were included in the derivation of equations (54) and (55).

$$\begin{split} g(\frac{\delta G_m}{G_m}) &= \frac{(C_{inv}/q)\sqrt{3WL/2\pi N_{sub}W_{dep}}}{\{\theta[1-\theta(\frac{C_{in}V_{in}}{C_{in}+C_f} + \frac{C_fV_f}{C_{in}+C_f} - V_t)]^{-1}} \\ &- 2(\frac{C_{in}V_{in}}{C_{in}+C_f} + \frac{C_fV_f}{C_{in}+C_f} - V_t)^{-1}\} \end{split} \tag{54}$$

$$\times \exp[\frac{3WL(C_{inv}\delta G_m/G_m)^2}{2N_{sub}W_{dep}q^2\{\theta[1-\theta(\frac{C_{in}V_{in}}{C_{in}+C_f} + \frac{C_fV_f}{C_{in}+C_f} - V_t)]^{-1}}] \\ &- 2(\frac{C_{in}V_{in}}{C_{in}+C_f} + \frac{C_fV_f}{C_{in}+C_f} - V_t)^{-1}\}^{-2} \end{split}$$

$$\sigma_{\frac{\Delta G_m}{G_m}}^2 = \frac{N_{sub} W_{dep} q^2}{3WLC_{inv}^2 \{\theta[1 - \theta(\frac{C_{in} V_{in}}{C_{in} + C_f} + \frac{C_f V_f}{C_{in} + C_f} - V_t)]^{-1}}$$

$$-2(\frac{C_{in} V_{in}}{C_{in} + C_f} + \frac{C_f V_f}{C_{in} + C_f} - V_t)^{-1}\}^{-2}$$

(55)

## 5.4 Computationally efficient statistical/variability aware simulation of FGMOSFET based circuit

The statistical parameters of  $\Delta X/X$  must be evaluated numerically without predetermining  $g(\delta X/X)$ . Among these parameters,  $\sigma^2_{\Delta X/X}$  has been often cited as it directly measures the magnitude of variability in X. Traditionally, numerical determination of  $\sigma^2_{\Delta X/X}$  must be performed using a Monte-Carlo simulation with numerous runs, numbering hundreds or thousands of runs.

Fortunately, determination of  $\sigma_{\Delta X/X}^2$  in the small signal analysis [45] based simulation, where the required computational cost is significantly lower than that of a conventional Monte-Carlo simulation, becomes possible using our  $f(\delta I_D/I_D)$ . This is because  $\sigma_{\Delta I_D/I_D}^2$  values are necessary inputs and can

be known in advance via applying  $f(\delta I_D/I_D)$  as discussed in the previous subsection. If we let the FG-MOSFET based circuit under consideration be composed of M FGMOSFETs,  $\sigma^2_{\Delta X/X}$  can be numerically determined using the following equation:

$$\sigma_{\frac{\Delta X}{X}}^2 = \sum_{m=1}^{M} \left[ \left( \frac{I_{Dm}}{X} S_{I_{Dm}}^X \right)^2 \sigma_{\frac{\Delta I_{Dm}}{I_{Dm}}}^2 \right]$$

(56)

where  $I_{Dm}$ ,  $S_{I_{Dm}}^X$  and  $\sigma_{\Delta I_{Dm}/I_{Dm}}^2$  denote the ideal drain current of an arbitrary m<sup>th</sup> FGMOSFET in the circuit in which all nonidealities have been neglected and the sensitivity of X with respect to  $I_{Dm}$ . Moreover,  $\sigma_{\Delta I_{Dm}/I_{Dm}}^2$  stands for  $\sigma_{\Delta I_{D}/I_{D}}^2$  of the m<sup>th</sup> FGMOSFET. It is notable that there exists no correlation terms in relationship (56). This is because  $\Delta I_{Dm}/I_{Dm}$  values are random variations that exhibit no spatial correlations [37]. According to [45],  $S_{I_{Dm}}^X$  which quantitatively represents the degree of dependency on  $I_{Dm}$  of X, can be mathematically defined as follows:

$$S_{I_{Dm}}^{X} = \frac{\partial X}{\partial I_{Dm}} \tag{57}$$

Since the whole set of  $S_{I_{Dm}}^X$  values can be obtained using sensitivity analysis in which the circuit under consideration requires only one calculation for its solution [45], the computational effort can be significantly reduced compared to a conventional Monte-Carlo simulation. Finally, since  $\sigma_{\Delta X/X}^2$  reflects the magnitude of variability in X, the following objective function can be satisfied using the optimum controllable parameters of the FGMOSFETs within the circuit.

$$\min[\sigma_{\Delta X/X}^2] \tag{58}$$

#### 6. CONCLUSIONS

In this research, an analytical probabilistic modelling of  $\Delta I_D$  of a FGMOSFET caused by manufacturing process variations has been proposed. The resulting models are in terms of a probability density function of  $\Delta I_D/I_D$ . Unlike [34], both the triode and saturation region operated FGMOSFETs were considered and the short channel effects taken into account. The resulting models have been found to be very accurate as they can fit the probabilistic distributions of  $\Delta I_D/I_D$  obtained from Monte-Carlo SPICE simulations of the 0.25  $\mu m$  level BSIM3v3 based candidate triode and saturation FGMOSFETs with very high accuracy. It was found that the variation of a saturation FGMOSFET is more severe. Moreover, the KS-tests were satisfied at a 99% confidence level. It was found that our resulting model for the saturation FGMOSFET was more accurate than those previously proposed [34].

Unlike the previous variance term models [33], sta-

tistical parameters and probabilities associated with  $\Delta I_D$  can be formulated for both the triode and saturation region operated FGMOSFETs using our results. With such parameters and probabilities, it was found that the occurrence of  $\Delta I_D$  is absolutely certain, which highlights the necessity of our work. Moreover, the impact of  $\Delta I_D$  upon the design tradeoffs associated with FGMOSFETs can be studied. Many objective functions that are conducive to the statistical/variability aware analysis and design, can be derived. Analytical probabilistic modelling and reduced computational effort for statistical/variability aware simulation of the FGMOSFET associated circuit can also be performed. Therefore our proposed probabilistic modelling of a FGMOSFET has been found to be useful for statistical/variability aware analysis and design of various FGMOSFET based circuits and systems. These have applications in many areas, e.g., signal processing [2], [3] dosimetry systems, [5], [6], biomedical engineering [7] and neural networks [21], [31], among others.

#### ACKNOWLEDGEMENT

The first author would like to acknowledge Mahidol University, Thailand, for their online database service, which served as a primary information resource.

#### References

- [1] G. Serrano, and P. Hasler, "A Floating Gate DAC Array," Proceeding of the 2004 International Symposium on Circuits and Systems (IS-CAS 04), pp. 357-360, 2004.

- [2] M. Drakaki, G. Fikos and S. Siskos, "Analog Signal Processing Circuits Using Floating Gate MOS Transistors," Proceedings of the International Conference on Technology and Automation (ICTA 05), pp. 322-327, 2005.

- [3] S. Sharma, S.S. Rajput, L.K. Mangotra and S.S. Jamuar, "Applications of A New FGMOS Based CCII in Low Voltage Analog Filters," *Indian Journal of Engineering and Materials Sciences*, Vol. 11, No. 5, pp. 397-400, 2004.

- [4] B. Ramasubramanian, "A New Wide Input-Range FGMOS Based Four Quadrant Multiplier with Electrical Error Correction," *Proceeding of* the 2007 International Symposium on Circuits and Systems (ISSCS 07), pp. 1-4, 2007.

- [5] Y. Wang, Y. Wang, G. Tarr and K. Iniewski, "A Temperature, Supply Voltage Compensated Floating-Gate MOS Dosimeter Using VTH Extractor," Proceeding of the 5th International Workshop on System-on-Chip for Real-Time Applications (IWSOC 05), pp 176-179, 2005.

- [6] Y. Wang, G. Tarr and Y. Wang, "A Novel Fully Integrated Floating-Gate MOSFET Radiation Dosimeter Using VTH Extractor," Proceeding of the 2<sup>nd</sup> Annual IEEE Northeast Workshop on

- Circuits and Systems (NEWCAS 04), pp 9-12, 2004.

- [7] P. Mejía-Chávez, J. C. Snchez-García, J. Velázquez-López, "Differential Difference Amplifier FGMOS for Electrocardiogram Signal Acquisition," Proceeding of the 2011 8<sup>th</sup> International Conference on Electrical Engineering Computing Science and Automatic Control (CCE 011), pp. 1-5, October 2011.

- [8] G. Kapur, S. Mittal, C. M. Markan and V.P. Pyara, "Analog Field Programmable CMOS Current Conveyor," Proceeding of the 2012 Students Conference on Engineering and Systems (SCES 12), pp. 1-6, 2012.

- [9] F. Khateb, N. Khatib and D. Kubánek, "Novel Ultra-Low-Power Class AB CCII+ Based on Floating-Gate Folded Cascode OTA," Circuits Systems and Signal Processing, Vol. 31, No. 2, pp. 447-464, 2012.

- [10] K. Gupta, M. Bhardwaj, B.P. Singh and R. Choudhary, "Design of Low Power Low Cost True RMS-to-DC Converter," Proceeding of the 2012 Second International Conference on Advanced Computing & Communication Technologies (ACCT 12), pp. 364-367, 2012.

- [11] R. Pandey and M. Gupta, "FGMOS Based Voltage-Controlled Grounded Resistor," *Radio Engineering*, Vol. 19, No. 3, pp. 455-459, 2010.

- [12] M. Gupta and R. Pandey, "Low-Voltage FG-MOS Based Analog Building Blocks," *Microelectronics Journal*, Vol. 42, No. 6, pp. 903-912, 2011.

- [13] M. Gupta and R. Pandey, "FGMOS Based Voltage-Controlled Resistor and Its Applications," *Microelectronics Journal*, Vol. 41, No. 1, pp. 25-32, 2010.

- [14] V Suresh Babu, P. S. Haseena and M. R. Baiju, "A Floating Gate MOSFET Based Current Reference with Subtraction Technique," Proceeding of the 2010 IEEE Computer Society Annual Symposium on VLSI (ISVLSI 10), pp. 206-209, 2010.

- [15] S. Siskos, "FGMOSFET Based Built-In Current Sensor for Low Supply Voltage Analog and Mixed-Signal Circuits Testing," Proceeding of the 2010 IEEE Computer Society Annual Symposium on VLSI (ISVLSI 10), pp. 259-264, 2010.

- [16] M-C J. Antonio, G-C Lizeth and G-C Felipe, "Floating-Gate MOSFET Parallel Analog Network for Assignment Problems," Proceeding of the 2010 7<sup>th</sup> International Conference on Electrical Engineering Computing Science and Automatic Control (CCE 10), pp. 556-559, 2010.

- [17] J. M. A. Miguel, A. J. Lopez-Martin, L. Acosta, J. Ramrez-Angulo, and R. G. Carvajal, "Using Floating Gate and Quasi-Floating Gate Techniques for Rail-To-Rail Tunable CMOS Transconductor Design," *IEEE Transactions on*

- Circuits and Systems I: Regular Papers, Vol. 58, No. 7, pp. 1604-1614, 2011.

- [18] A. J. Lopez-Martin, J. Ramrez-Angulo, R. G. Carvajal, and L. Acosta, "CMOS Transconductors with Continuous Tuning Using FGMOS Balanced Output Current Scaling," *IEEE Journal of Solid-State Circuits*, Vol. 43, No. 5, pp. 1313-1323, 2008.

- [19] V. Srinivasan, G. Serrano, C. M. Twigg, and P. Hasler, "A Floating-Gate-Based Programmable CMOS Reference," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 55, No. 11, pp. 3448-3456, 2008.

- [20] Y. L. Wong, M. H. Cohen and P. A. Abshire, "A Floating-Gate Comparator with Automatic Offset Adaptation for 10-bit Data Conversion," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 52, No. 7, pp. 1316-1326, 2005.

- [21] Y. L. Wong, P. Xu, and P. Abshire, "Ultra-Low Spike Rate Silicon Neuron," Proceeding of the 2007 IEEE Biomedical Circuits and Systems Conference (BioCAS 07), pp. 95-98, November 2007.

- [22] K. Hasegawa, M. Aoki, T. Yamawaki, S. Tanaka, "Modelling Transistor Variation Using α-Power Formula and Its application to Sensitivity Analysis on Harmonic Distortion in Differential Amplifier," Analog Integrated Circuits and Signal Processing, Vol. 72, No. 3, pp. 605-613, 2011.

- [23] H. Masuda, T. Kida and S. Ohkawa, "Comprehensive Matching Characterization of Analog CMOS Circuits," *IEICE Transaction on Fundamental of Electronics, Communications and Computer Sciences*, Vol. E92-A, No. 4, pp. 966-975, 2009.

- [24] S. Vlassis, S. Siskos, "Current-Mode Non-Linear Building Blocks Based on Floating-Gate Transistors," *Proceeding of the 2000 International Sym*posium on Circuits and Systems (ISCAS 00), pp. 521-524, 2000.

- [25] C. Y. Kwok and H. R. Merhrvarz, "Low Voltage and Mismatch Analysis of Quadruple Source Coupled Multi-input Floating-Gate MOSFET Multiplier with Offset Trimming," Analog Integrated Circuits and Signal Processing, Vol. 26, No. 2, pp. 141-156, 2001.

- [26] S. Vlassis and S. Siskos, "Design of Voltage-Mode and Current-Mode Computational Circuits Using Floating-Gate MOS Transistors," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 51, No. 2, pp. 329-341, 2004.

- [27] A. El mourabit, P. Pittet, G. N. Lu, "A wide-linear range subthreshold OTA based on FG-MOS transistor," Proceedings of the 2004 11<sup>th</sup> IEEE International Conference on Electronics, Circuits and Systems (ICECS 04), pp. 17-20, 2004.

- [28] A. El mourabit, P. Pittet, G. N. Lu, "A low voltage highly linear CMOS OTA," *Proceedings. The* 16<sup>th</sup> International Conference on Microelectronics (ICM 04), pp. 700-703, 2004.

- [29] S. Vlassis and S. Siskos, "Differential-Voltage Attenuator Based on Floating-Gate MOS Transistors and Its Applications," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, Vol. 48, No. 11, pp. 1372-1378, 2001.

- [30] Y. Zhai and P. A. Abshire, "Adaptive Log Domain Filters for System Identification Using Floating Gate Transistors," *Analog Integrated Circuits and Signal Processing*, Vol. 56, No. 1, pp. 23-36, 2008.

- [31] V. Suresh Babu, Salini Devi R., Ambika Sekhar and M. R. Baiju, "FGMOSFET Circuit for Neuron Activation Function and Its Derivative," Proceeding of the 2009 4<sup>th</sup> IEEE Conference on Industrial Electronics and Applications (ICIEA 09), pp. 739-744, 2009.

- [32] J. Alfredsson and S. Aunet, "Trade-offs for high yield in 90 nm subthreshold floating-gate circuits by Monte-Carlo simulations," *Proceedings* of IFIP VLSI-SOC Conference 2008 (VLSI-SOC 08), pp. 1-4, 2008.

- [33] R. Banchuin, "Analytical Model of Random Variation in Drain Current of FGMOSFET," Active and Passive Electronic Components, Vol. 2015, pp. 1-12, 2015.

- [34] R. Banchuin and R. Chaisricharoen, "The probabilistic modeling of random variation in FG-MOSFET," Proceedings of the 2016 13<sup>th</sup> International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON'16), pp. 1-5, 2016.

- [35] Y. Ye, S. Gummalla, C.-C.Wang, C. Chakrabarti and Y. Cao, "Random Variability Modeling and Its Impact on Scaled CMOS Circuits," *Journal* of Computational Electronics, Vol. 9, No. 3, pp. 108-113, 2010.

- [36] S. Bhunia and S. Mukhopadhyay, Low Power Variation Tolerant and Design in Nanometer Silicon, Springer Science+Business Media, LLC, New York, 2011, ch. 1.

- [37] K. Takeuchi, A. Nishida and T. Hiramoto, "Random Fluctuations in Scaled MOS Devices," Proceeding of the 2009 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD 09), pp. 79-85, 2009.

- [38] T. Mogami, "Perspective of CMOS Technology and Future Requirement," Proceedings of SPIE, the International Society for Optical Engineering, pp. 774802-1-774802-9, 2010.

- [39] J. Ramirez-Angulo, G. Gonzlrlez-Altamirano and S. C. Choi, "Modelling Multiple-Input Floating-Gate Transistors for Analog Signal Pro-

- cessing," Proceeding of the 1997 International Symposium on Circuits and Systems (ISCAS 97), pp. 2020-2023, 1997.

- [40] T. Altiok and B. Melamed, Simulation Modelling and Analysis with ARENA, Elsevier, Inc., United States, 2007, ch. 8.

- [41] S.A. Klugman, H.H Panjer and G.E. Willmot, Loss Models: From Data to Decisions, John Wiley and Sons, Inc., United States, 2008, ch. 13.

- [42] W.W. Hines, D.C. Montgomery, D.M. Goldsman and C.M. Borror, *Probability and Statistics in Engineering*, John Wiley and Sons, Inc., United States, 2003, ch. 3.

- [43] C. Forbes, M. Evans, N. Hastings and B. Peacock, Statistical Distributions, 4<sup>th</sup> ed., John Wiley and Sons, Inc., New York, 2011, ch. 2.

- [44] A.S. Medina-Vazquez, J. de la Cruz-Alejo, F. Gomez-Castaneda and J. A. Moreno-Cadenas, "Low-Voltage Linear Transconductor and A memory Current Using The MIFGMOS Transistor," *International Journal of Electronics*, Vol. 96, No. 9, pp. 895-914, 2009.

- [45] G. Cijan, T. Tuma and A. Burmen, "Modelling and Simulation of MOS Transistor Mismatch," Proceeding of the 6th Eurosim Congress on Mod-

eling and Simulation (EUROSIM 07), pp. 1-8, 2007.

Rawid Banchuin received the B.Eng. degree in electrical engineering from Mahidol University, Bangkok, Thailand in 2000, the degree of M.Eng. in computer engineering and Ph.D. in electrical and computer engineering from King Mongkut's University of Technology Thonburi, Bangkok, Thailand in 2003 and 2008 respectively. He was with the Department of Electrical Engineering, Rajamangala Institute of Technol-

ogy, North-Bangkok Campus since 2003. At the present, he is with the Faculty of Engineering and Graduated School of Information Technology, Siam University, Bangkok, Thailand. Asst. Prof. Dr. Rawid Banchuin is a member of IEEE and council of engineer (Thailand) and has joined the technical program committee of International ECTI Northern Section Conference on Electrical, Electronics, Computer and Telecommunications Engineering (ECTI-NCON), since 2017.

Roungsan Chaisricharoen received B.Eng., M.Eng. and Ph.D. degrees from the department of computer engineering, King Mongkut's University of Technology Thonburi, Bangkok, Thailand. He is an assistant professor at the school of information technology, Mae Fah Luang University, Chiang Rai, Thailand. His research interests are computational intelligence, analog circuits and devices, wireless networks and optimization technology.

niques